# Intel<sup>®</sup> I/O Controller Hub 7 (ICH7)/Intel<sup>®</sup> High Definition Audio/AC'97

**Programmer's Reference Manual (PRM)**

For the Intel<sup>®</sup> 82801GB ICH7 and 82801GR ICH7R I/O Controller Hubs

**April 2005**

Document Number: 307017-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> I/O Controller Hub 7 (ICH7) Family chipset component may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM.

Intel, Intel SpeedStep, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation

| 1 | Intel <sup>®</sup> | High D               | efinition Audio Controller Registers (D27:F0)                               | 13 |

|---|--------------------|----------------------|-----------------------------------------------------------------------------|----|

|   | 1.1                | Intel <sup>®</sup> F | High Definition Audio PCI Configuration Space                               |    |

|   |                    | (Intel <sup>®</sup>  | High Definition Audio— D27:F0)                                              | 13 |

|   |                    | 1.1.1                | VID—Vendor Identification Register                                          |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 15 |

|   |                    | 1.1.2                | DID—Device Identification Register                                          |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 15 |

|   |                    | 1.1.3                | PCICMD—PCI Command Register                                                 |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 16 |

|   |                    | 1.1.4                | PCISTS—PCI Status Register                                                  |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 17 |

|   |                    | 1.1.5                | RID—Revision Identification Register                                        |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 17 |

|   |                    | 1.1.6                | PI—Programming Interface Register                                           |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 18 |

|   |                    | 1.1.7                | SCC—Sub Class Code Register                                                 |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 18 |

|   |                    | 1.1.8                | BCC—Base Class Code Register                                                |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 18 |

|   |                    | 1.1.9                | CLS—Cache Line Size Register                                                |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 18 |

|   |                    | 1.1.10               | LT—Latency Timer Register                                                   |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 19 |

|   |                    | 1.1.11               | HEADTYP—Header Type Register                                                |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 19 |

|   |                    | 1.1.12               | HDBARL—Intel® High Definition Audio Lower Base Address Register             |    |

|   |                    |                      | (Intel® High Definition Audio—D27:F0)                                       | 19 |

|   |                    | 1.1.13               | HDBARU—Intel <sup>®</sup> High Definition Audio Upper Base Address Register |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 19 |

|   |                    | 1.1.14               | SVID—Subsystem Vendor Identification Register                               |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 20 |

|   |                    | 1.1.15               | SID—Subsystem Identification Register                                       |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 20 |

|   |                    | 1.1.16               | CAPPTR—Capabilities Pointer Register (Audio—D30:F2)                         | 21 |

|   |                    | 1.1.17               | INTLN—Interrupt Line Register                                               |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 21 |

|   |                    | 1.1.18               | INTPN—Interrupt Pin Register                                                |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 21 |

|   |                    | 1.1.19               | HDCTL—Intel <sup>®</sup> High Definition Audio Control Register             |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 22 |

|   |                    | 1.1.20               | TCSEL—Traffic Class Select Register                                         |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 23 |

|   |                    | 1.1.21               | DCKSTS—Docking Status Register                                              |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 24 |

|   |                    | 1.1.22               | PID—PCI Power Management Capability ID Register                             |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 24 |

|   |                    | 1.1.23               | PC—Power Management Capabilities Register                                   |    |

|   |                    |                      | (Intel® High Definition Audio Controller—D27:F0)                            | 25 |

| 1.1.24 | PCS—Power Management Control and Status Register                            |     |

|--------|-----------------------------------------------------------------------------|-----|

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 25  |

| 1.1.25 | MID—MSI Capability ID Register                                              |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 26  |

| 1.1.26 | MMC—MSI Message Control Register                                            |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 26  |

| 1.1.27 | MMLA—MSI Message Lower Address Register                                     |     |

| 1.1.21 | (Intel® High Definition Audio Controller—D27:F0)                            | 27  |

| 1.1.28 | MMUA—MSI Message Upper Address Register                                     | 2 1 |

| 1.1.20 | (Intel® High Definition Audio Controller—D27:F0)                            | 27  |

| 4 4 00 |                                                                             | ∠1  |

| 1.1.29 | MMD—MSI Message Data Register                                               | 0-  |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 21  |

| 1.1.30 | PXID—PCI Express* Capability ID Register                                    |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 21  |

| 1.1.31 | PXC—PCI Express* Capabilities Register                                      |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 28  |

| 1.1.32 | DEVCAP—Device Capabilities Register                                         |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 28  |

| 1.1.33 | DEVC—Device Control Register                                                |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 29  |

| 1.1.34 | DEVS—Device Status Register                                                 |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 29  |

| 1.1.35 |                                                                             |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 30  |

| 1.1.36 | PVCCAP1—Port VC Capability Register 1                                       |     |

| 1.1.50 | (Intel® High Definition Audio Controller—D27:F0)                            | 30  |

| 1.1.37 |                                                                             |     |

| 1.1.57 | (Intel® High Definition Audio Controller—D27:F0)                            | 21  |

| 1.1.38 | PVCCTL — Port VC Control Register                                           | 5   |

| 1.1.30 | (Into B High Definition Audio Controller D27:E0)                            | 21  |

| 4 4 00 | (Intel® High Definition Audio Controller—D27:F0)                            | o   |

| 1.1.39 | PVCSTS—Port VC Status Register                                              | ~   |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 3   |

| 1.1.40 | VC0CAP—VC0 Resource Capability Register                                     |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 32  |

| 1.1.41 | VC0CTL—VC0 Resource Control Register                                        |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 32  |

| 1.1.42 | VC0STS—VC0 Resource Status Register                                         |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 32  |

| 1.1.43 | VCiCAP—VCi Resource Capability Register                                     |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 33  |

| 1.1.44 | VCiCTL—VCi Resource Control Register                                        |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 33  |

| 1.1.45 | VCiSTS—VCi Resource Status Register                                         |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 34  |

| 1.1.46 | RCCAP—Root Complex Link Declaration Enhanced                                |     |

|        | Capability Header Register (Intel® High Definition Audio Controller—D27:F0) | 34  |

| 1.1.47 | . , , , , , , , , , , , , , , , , , , ,                                     |     |

|        | (Intel® High Definition Audio Controller—D27:F0)                            | 34  |

| 1.1.48 | L1DESC—Link 1 Description Register                                          | 5-  |

| 1.1.+0 | (Intel® High Definition Audio Controller—D27:F0)                            | 35  |

| 1 1 10 | L1ADDL—Link 1 Lower Address Register                                        | 00  |

| 1.1.49 | (Intel® High Definition Audio Controller—D27:F0)                            | 2.5 |

|        | TITLE: FIIGH DEHINITOH AUGIO CONTONIEI—DZ1.FU)                              | ა:  |

|     | 1.1.50               | L1ADDU—Link 1 Upper Address Register (Intel® High Definition Audio Controller—D27:F0) | 31  |

|-----|----------------------|---------------------------------------------------------------------------------------|-----|

| 1.2 | Intel <sup>®</sup> H | ligh Definition Audio Memory Mapped Configuration Registers                           |     |

|     |                      | High Definition Audio— D27:F0)                                                        | 36  |

|     | 1.2.1                | GCAP—Global Capabilities Register                                                     |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 40  |

|     | 1.2.2                | VMIN—Minor Version Register                                                           |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 40  |

|     | 1.2.3                | VMAJ—Major Version Register                                                           |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 40  |

|     | 1.2.4                | OUTPAY—Output Payload Capability Register                                             |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 41  |

|     | 1.2.5                | INPAY—Input Payload Capability Register                                               |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 41  |

|     | 1.2.6                | GCTL—Global Control Register                                                          |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 42  |

|     | 1.2.7                | WAKEEN—Wake Enable Register                                                           |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 43  |

|     | 1.2.8                | STATESTS—State Change Status Register                                                 |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 43  |

|     | 1.2.9                | GSTS—Global Status Register                                                           |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 44  |

|     | 1.2.10               | OUTSTRMPAY—Output Stream Payload Capability                                           | 4.  |

|     | 4044                 | (Intel® High Definition Audio Controller—D27:F0)                                      | 44  |

|     | 1.2.11               | INSTRMPAY—Input Stream Payload Capability                                             | 4.5 |

|     | 4 0 40               | (Intel® High Definition Audio Controller—D27:F0)                                      | 40  |

|     | 1.2.12               | INTCTL—Interrupt Control Register (Intel® High Definition Audio Controller—D27:F0)    | 16  |

|     | 1 0 10               | INTSTS—Interrupt Status Register                                                      | 40  |

|     | 1.2.13               | (Intel® High Definition Audio Controller—D27:F0)                                      | 47  |

|     | 1 2 1/               | WALCLK—Wall Clock Counter Register                                                    | 47  |

|     | 1.2.17               | (Intel® High Definition Audio Controller—D27:F0)                                      | 47  |

|     | 1 2 15               | SSYNC—Stream Synchronization Register                                                 | 7   |

|     | 1.2.10               | (Intel® High Definition Audio Controller—D27:F0)                                      | 48  |

|     | 1 2 16               | CORBLBASE—CORB Lower Base Address Register                                            | (   |

|     | 1.2.10               | (Intel® High Definition Audio Controller—D27:F0)                                      | 48  |

|     | 1 2 17               | CORBUBASE—CORB Upper Base Address Register                                            |     |

|     | 1.2.17               | (Intel® High Definition Audio Controller—D27:F0)                                      | 49  |

|     | 1.2.18               | CORBWP—CORB Write Pointer Register                                                    |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 49  |

|     | 1.2.19               | CORBRP—CORB Read Pointer Register                                                     |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 49  |

|     | 1.2.20               | CORBCTL—CORB Control Register                                                         |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 50  |

|     | 1.2.21               | CORBST—CORB Status Register                                                           |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 50  |

|     | 1.2.22               | CORBSIZE—CORB Size Register                                                           |     |

|     | <b></b>              | Intel® High Definition Audio Controller—D27:F0)                                       | 50  |

|     | 1.2.23               | RIRBLBASE—RIRB Lower Base Address Register                                            |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 51  |

|     | 1.2.24               | RIRBUBASE—RIRB Upper Base Address Register                                            |     |

|     |                      | (Intel® High Definition Audio Controller—D27:F0)                                      | 51  |

|     |                      |                                                                                       |     |

|   | 1.2.2          | 5 RIRBWP—RIRB Write Pointer Register                                                                                                             | <b>5</b> 4 |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   | 1.2.2          | (Intel <sup>®</sup> High Definition Audio Controller—D27:F0)                                                                                     | 51         |

|   |                | (Intel <sup>®</sup> High Definition Audio Controller—D27:F0)                                                                                     | 52         |

|   | 1.2.2          | 7 RIRBCTL—RIRB Control Register (Intel® High Definition Audio Controller—D27:F0)                                                                 | <b>5</b> 2 |

|   | 1.2.2          | 8 RIRBSTS—RIRB Status Register                                                                                                                   |            |

|   |                | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 53         |

|   | 1.2.2          | 9 RIRBSIZE—RIRB Size Register                                                                                                                    | 50         |

|   | 123            | (Intel <sup>®</sup> High Definition Audio Controller—D27:F0)                                                                                     | 53         |

|   | 1.2.3          | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 53         |

|   | 1.2.3          | 1 IR—Immediate Response Register                                                                                                                 |            |

|   |                | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 54         |

|   | 1.2.3          | 2 IRS—Immediate Command Status Register (Intel® High Definition Audio Controller—D27:F0)                                                         | <b>-</b> 4 |

|   | 122            | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 54         |

|   | 1.2.3          | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 55         |

|   | 1.2.3          | 4 DPUBASE—DMA Position Upper Base Address Register                                                                                               |            |

|   |                | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 55         |

|   | 1.2.3          | 5 SDCTL—Stream Descriptor Control Register (Intel® High Definition Audio Controller—D27:F0)                                                      |            |

|   | 122            | 6 SDSTS—Stream Descriptor Status Register                                                                                                        | 55         |

|   | 1.2.3          | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 57         |

|   | 1.2.3          | 7 SDLPIB—Stream Descriptor Link Position in Buffer                                                                                               |            |

|   |                | Register (Intel® High Definition Audio Controller—D27:F0)                                                                                        | 58         |

|   | 1.2.3          |                                                                                                                                                  | 50         |

|   | 1.2.3          | (Intel <sup>®</sup> High Definition Audio Controller—D27:F0)                                                                                     | 58         |

|   | 1.2.3          | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 59         |

|   | 1.2.4          | 0 SDEJEOW—Stream Descriptor EJEO Watermark Register                                                                                              |            |

|   |                | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 59         |

|   | 1.2.4          |                                                                                                                                                  |            |

|   | 1 2 4          | (Intel <sup>®</sup> High Definition Audio Controller—D27:F0)                                                                                     | 60         |

|   | 1.2.4          | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 61         |

|   | 1.2.4          | 3 SDBDPL—Stream Descriptor Buffer Descriptor List Pointer Lower Base A                                                                           | ddress     |

|   |                | Register                                                                                                                                         |            |

|   |                | (Intel® High Definition Audio Controller—D27:F0)                                                                                                 | 62         |

|   | 1.2.4          | 4 SDBDPU—Stream Descriptor Buffer Descriptor List Pointer<br>Upper Base Address Register (Intel <sup>®</sup> High Definition Audio Controller—D2 | 7·E0\ 62   |

|   |                |                                                                                                                                                  | ,          |

| 2 | AC '97 Aud     | lio Controller Registers (D30:F2)                                                                                                                | 63         |

|   |                | 77 Audio PCI Configuration Space                                                                                                                 |            |

|   | `              | 0—D30:F2)                                                                                                                                        |            |

|   | 2.1.1<br>2.1.2 | <b>5</b> \ ,                                                                                                                                     |            |

|   | 2.1.2          |                                                                                                                                                  |            |

|   | 2.1.3          | e ,                                                                                                                                              |            |

|   | 2.1.5          |                                                                                                                                                  |            |

|   | 2.1.6          | e i                                                                                                                                              |            |

|   | 2.1.7          |                                                                                                                                                  |            |

|   |                |                                                                                                                                                  |            |

|   |      | 2.1.8  | BCC—Base Class Code Register (Audio—D30:F2)                                |    |

|---|------|--------|----------------------------------------------------------------------------|----|

|   |      | 2.1.9  | HEADTYP—Header Type Register (Audio—D30:F2)                                | 68 |

|   |      | 2.1.10 | NAMBAR—Native Audio Mixer Base Address Register (Audio—D30:F2)             | 68 |

|   |      | 2.1.11 | NABMBAR—Native Audio Bus Mastering Base Address Register (Audio—D30:F2)    | 69 |

|   |      | 2.1.12 |                                                                            | 69 |

|   |      | 2.1.13 | MBBAR—Bus Master Base Address Register (Audio—D30:F2)                      |    |

|   |      | 2.1.14 | SVID—Subsystem Vendor Identification Register (Audio—D30:F2)               |    |

|   |      | 2.1.15 | SID—Subsystem Identification Register (Audio—D30:F2)                       |    |

|   |      | 2.1.16 | CAP_PTR—Capabilities Pointer Register (Audio—D30:F2)                       | 71 |

|   |      |        | INT_LN—Interrupt Line Register (Audio—D30:F2)                              |    |

|   |      | 2.1.18 | INT_PN—Interrupt Pin Register (Audio—D30:F2)                               | 72 |

|   |      | 2.1.19 | PCID—Programmable Codec Identification Register (Audio—D30:F2)             | 72 |

|   |      |        | CFG—Configuration Register (Audio—D30:F2)                                  | 72 |

|   |      |        | PID—PCI Power Management Capability Identification Register (Audio—D30:F2) | 73 |

|   |      |        | PC—Power Management Capabilities Register (Audio—D30:F2)                   | 73 |

|   |      |        | PCS—Power Management Control and Status Register (Audio—D30:F2)            | 74 |

|   | 2.2  | AC '97 | Audio I/O Space (D30:F2)                                                   | 75 |

|   |      | 2.2.1  | x_BDBAR—Buffer Descriptor Base Address Register                            |    |

|   |      |        | (Audio—D30:F2)                                                             |    |

|   |      | 2.2.2  | x_CIV—Current Index Value Register (Audio—D30:F2)                          |    |

|   |      | 2.2.3  | x_LVI—Last Valid Index Register (Audio—D30:F2)                             |    |

|   |      | 2.2.4  | x_SR—Status Register (Audio—D30:F2)                                        | 80 |

|   |      | 2.2.5  | x_PICB—Position In Current Buffer Register (Audio—D30:F2)                  |    |

|   |      | 2.2.6  | x_PIV—Prefetched Index Value Register (Audio—D30:F2)                       |    |

|   |      | 2.2.7  | x_CR—Control Register (Audio—D30:F2)                                       |    |

|   |      | 2.2.8  | GLOB_CNT—Global Control Register (Audio—D30:F2)                            |    |

|   |      | 2.2.9  | GLOB_STA—Global Status Register (Audio—D30:F2)                             |    |

|   |      | 2.2.10 | ,                                                                          |    |

|   |      | 2.2.11 | SDM—SDATA_IN Map Register (Audio—D30:F2)                                   | 87 |

| 3 | AC ' |        | m Controller Registers (D30:F3)                                            |    |

|   | 3.1  | AC '97 | Modem PCI Configuration Space (D30:F3)                                     |    |

|   |      | 3.1.1  | VID—Vendor Identification Register (Modem—D30:F3)                          |    |

|   |      | 3.1.2  | DID—Device Identification Register (Modem—D30:F3)                          |    |

|   |      | 3.1.3  | PCICMD—PCI Command Register (Modem—D30:F3)                                 |    |

|   |      | 3.1.4  | PCISTS—PCI Status Register (Modem—D30:F3)                                  |    |

|   |      | 3.1.5  | RID—Revision Identification Register (Modem—D30:F3)                        |    |

|   |      | 3.1.6  | PI—Programming Interface Register (Modem—D30:F3)                           |    |

|   |      | 3.1.7  | SCC—Sub Class Code Register (Modem—D30:F3)                                 |    |

|   |      | 3.1.8  | BCC—Base Class Code Register (Modem—D30:F3)                                |    |

|   |      | 3.1.9  | HEADTYP—Header Type Register (Modem—D30:F3)                                | 93 |

|   |      | 3.1.10 | MMBAR—Modem Mixer Base Address Register                                    |    |

|   |       |                      | (Modem—D30:F3)                                                                   |     |

|---|-------|----------------------|----------------------------------------------------------------------------------|-----|

|   |       | 3.1.11               | MBAR—Modem Base Address Register (Modem—D30:F3)                                  | 94  |

|   |       | 3.1.12               | SVID—Subsystem Vendor Identification Register                                    |     |

|   |       |                      | (Modem—D30:F3)                                                                   | 94  |

|   |       |                      | SID—Subsystem Identification Register (Modem—D30:F3)                             |     |

|   |       |                      | CAP_PTR—Capabilities Pointer Register (Modem—D30:F3)                             |     |

|   |       | 3.1.15               | INT_LN—Interrupt Line Register (Modem—D30:F3)                                    | 95  |

|   |       | 3.1.16               | INT_PIN—Interrupt Pin Register (Modem—D30:F3)                                    | 96  |

|   |       | 3.1.17               | PID—PCI Power Management Capability Identification                               |     |

|   |       |                      | Register (Modem—D30:F3)                                                          | 96  |

|   |       | 3.1.18               |                                                                                  |     |

|   |       |                      | (Modem—D30:F3)                                                                   | 96  |

|   |       | 3.1.19               | PCS—Power Management Control and Status Register                                 |     |

|   |       |                      | (Modem—D30:F3)                                                                   | 97  |

|   | 3.2   |                      | Modem I/O Space (D30:F3)                                                         | 98  |

|   |       | 3.2.1                | x_BDBAR—Buffer Descriptor List Base Address Register                             |     |

|   |       |                      | (Modem—D30:F3)                                                                   | 100 |

|   |       | 3.2.2                | x_CIV—Current Index Value Register (Modem—D30:F3)                                |     |

|   |       | 3.2.3                | x_LVI—Last Valid Index Register (Modem—D30:F3)                                   |     |

|   |       | 3.2.4                | x_SR—Status Register (Modem—D30:F3)                                              | 101 |

|   |       | 3.2.5                | x_PICB—Position in Current Buffer Register                                       |     |

|   |       |                      | (Modem—D30:F3)                                                                   | 102 |

|   |       | 3.2.6                | x_PIV—Prefetch Index Value Register                                              | 400 |

|   |       | 0.07                 | (Modem—D30:F3)                                                                   |     |

|   |       | 3.2.7                | x_CR—Control Register (Modem—D30:F3)                                             |     |

|   |       | 3.2.8                | GLOB_CNT—Global Control Register (Modem—D30:F3)                                  |     |

|   |       | 3.2.9                | GLOB_STA—Global Status Register (Modem—D30:F3)                                   | 105 |

|   |       | 3.2.10               | CAS—Codec Access Semaphore Register (Modem—D30:F3)                               | 40- |

|   |       |                      | ,                                                                                |     |

| 4 | Intel | ® High D             | efinition Audio BIOS Considerations                                              | 109 |

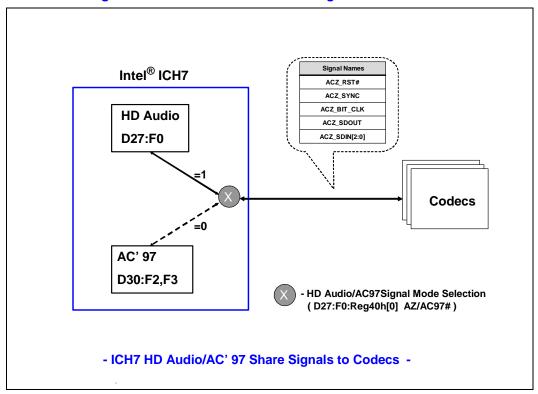

|   | 4.1   | Intel <sup>®</sup> F | High Definition Audio/AC' 97 Signal Mode Selection                               | 109 |

|   |       | 4.1.1                | Intel® High Definition Audio/AC' 97 Codec Detection                              |     |

|   |       | 4.1.2                | Intel® High Definition Audio Codec Initialization                                |     |

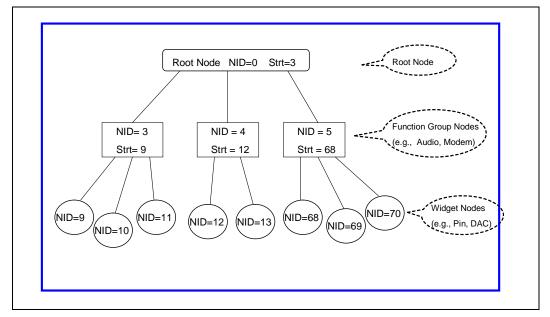

|   |       |                      | 4.1.2.1 Intel <sup>®</sup> High Definition Audio Codec Architecture Introduction |     |

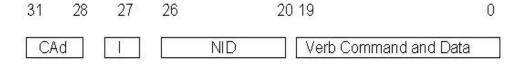

|   |       |                      | 4.1.2.2 Codec Verb Table                                                         |     |

|   |       |                      | 4.1.2.3 Codec Initialization Programming Sequence                                |     |

|   |       |                      | 4.1.2.4 Codec Initialization Sample Code                                         |     |

|   |       | 4.1.3                | Intel® High Definition Audio Codec Initialization on S3 Resume                   |     |

|   | 4.2   | Intel <sup>®</sup> F | ligh Definition Audio Controller Configuration                                   |     |

|   | 4.3   | Intel <sup>®</sup> F | High Definition Audio PME Event                                                  | 126 |

|   |       |                      |                                                                                  |     |

#### **Figures**

| 4-1  | Intel® ICH7 High Definition Audio/AC' 97 Share Signals to Codecs | 109 |

|------|------------------------------------------------------------------|-----|

| 4-2  | Intel® High Definition Audio Codec Node Structure and Addressing | 113 |

|      |                                                                  |     |

| Гabl | es                                                               |     |

| 1-1  | Intel® High Definition Audio PCI Register Address Map            |     |

|      | (Intel® High Definition Audio D27:F0)                            | 13  |

| 1-2  | Intel® High Definition Audio PCI Register Address Map            |     |

|      | (Intel® High Definition Audio D27:F0)                            | 36  |

| 2-1  | AC '97 Audio PCI Register Address Map (Audio—D30:F2)             |     |

| 2-2  | Intel® ICH7 Audio Mixer Register Configuration                   | 75  |

| 2-3  | Native Audio Bus Master Control Registers                        | 77  |

| 3-1  | AC '97 Modem PCI Register Address Map (Modem—D30:F3)             | 89  |

| 3-2  | Intel® ICH7 Modem Mixer Register Configuration                   | 98  |

|      | Modem Registers                                                  |     |

|      |                                                                  |     |

# **Revision History**

| Revision | Description     | Date       |

|----------|-----------------|------------|

| -001     | Initial release | April 2005 |

8

# 1 Intel® High Definition Audio Controller Registers (D27:F0)

The Intel® HD Audio controller resides in PCI Device 27, Function 0 on bus 0. This function contains a set of DMA engines that are used to move samples of digitally encoded data between system memory and external codecs.

Note: All registers in this function (including memory-mapped registers) must be addressable in byte, word, and DWord quantities. The software must always make register accesses on natural boundaries (i.e. DWord accesses must be on DWord boundaries; word accesses on word boundaries, etc.) In addition, the memory-mapped register space must not be accessed with the LOCK semantic exclusive-access mechanism. If software attempts exclusive-access mechanisms to the Intel® HD Audio memory-mapped space, the results are undefined.

**Note:** Users interested in providing feedback on the Intel<sup>®</sup> HD Audio specification or planning to implement the Intel<sup>®</sup> High Definition Audio specification into a future product will need to execute the *Intel<sup>®</sup> High Definition Audio Specification Developer's Agreement*. For more information, contact nextgenaudio@intel.com.

# 1.1 Intel<sup>®</sup> High Definition Audio PCI Configuration Space (Intel<sup>®</sup> High Definition Audio— D27:F0)

*Note:* Address locations that are not shown should be treated as Reserved.

Table 1-1. Intel<sup>®</sup> High Definition Audio PCI Register Address Map (Intel<sup>®</sup> High Definition Audio D27:F0)

| Offset  | Mnemonic | Register Name                                            | Default                   | Access   |

|---------|----------|----------------------------------------------------------|---------------------------|----------|

| 00h–01h | VID      | Vendor Identification                                    | 8086h                     | RO       |

| 02h-03h | DID      | Device Identification                                    | See register description. | RO       |

| 04h-05h | PCICMD   | PCI Command                                              | 0000h                     | R/W, RO  |

| 06h-07h | PCISTS   | PCI Status                                               | 0010h                     | R/WC, RO |

| 08h     | RID      | Revision Identification                                  | See register description. | RO       |

| 09h     | PI       | Programming Interface                                    | 00h                       | RO       |

| 0Ah     | SCC      | Sub Class Code                                           | 03h                       | RO       |

| 0Bh     | BCC      | Base Class Code                                          | 04h                       | RO       |

| 0Ch     | CLS      | Cache Line Size                                          | 00h                       | R/W      |

| 0Dh     | LT       | Latency Timer                                            | 00h                       | RO       |

| 0Eh     | HEADTYP  | Header Type                                              | 00h                       | RO       |

| 10h–13h | HDBARL   | Intel® High Definition Audio Lower Base Address (Memory) | 00000004h                 | R/W, RO  |

Table 1-1. Intel<sup>®</sup> High Definition Audio PCI Register Address Map (Intel<sup>®</sup> High Definition Audio D27:F0)

| 14h–17h   | HDBARU  | Intel® High Definition Audio Upper Base Address (Memory) | 00000000h                   | R/W              |

|-----------|---------|----------------------------------------------------------|-----------------------------|------------------|

| 2Ch-2Dh   | SVID    | Subsystem Vendor Identification                          | 0000h                       | R/WO             |

| 2Eh-2Fh   | SID     | Subsystem Identification                                 | 0000h                       | R/WO             |

| 34h       | CAPPTR  | Capability List Pointer                                  | 50h                         | RO               |

| 3Ch       | INTLN   | Interrupt Line                                           | 00h                         | R/W              |

| 3Dh       | INTPN   | Interrupt Pin                                            | See Register<br>Description | RO               |

| 40h       | HDCTL   | Intel High Definition Audio Control                      | 00h                         | R/W, RO          |

| 44h       | TCSEL   | Traffic Class Select                                     | 00h                         | R/W              |

| 4Dh       | DCKSTS  | Docking Status                                           | 80h                         | R/WO, RO         |

| 50h–51h   | PID     | PCI Power Management Capability ID                       | 6001h                       | RO               |

| 52h-53h   | PC      | Power Management Capabilities                            | C842                        | RO               |

| 54h–57h   | PCS     | Power Management Control and Status                      | 00000000h                   | R/W, RO,<br>R/WC |

| 60h–61h   | MID     | MSI Capability ID                                        | 7005h                       | RO               |

| 62h–63h   | MMC     | MSI Message Control                                      | 0080h                       | R/W, RO          |

| 64h–67h   | MMLA    | MSI Message Lower Address                                | 00000000h                   | R/W, RO          |

| 68h–6Bh   | MMUA    | SMI Message Upper Address                                | 00000000h                   | R/W              |

| 6Ch-6Dh   | MMD     | MSI Message Data                                         | 0000h                       | R/W              |

| 70h–71h   | PXID    | PCI Express* Capability Identifiers                      | 0010h                       | RO               |

| 72h–73h   | PXC     | PCI Express Capabilities                                 | 0091h                       | RO               |

| 74h–77h   | DEVCAP  | Device Capabilities                                      | 00000000h                   | RO, R/WO         |

| 78h–79h   | DEVC    | Device Control                                           | 0800h                       | R/W, RO          |

| 7Ah–7Bh   | DEVS    | Device Status                                            | 0010h                       | RO               |

| 100h-103h | VCCAP   | Virtual Channel Enhanced Capability Header               | 13010002h                   | RO               |

| 104h–107h | PVCCAP1 | Port VC Capability Register 1                            | 00000001h                   | RO               |

| 108h-10Bh | PVCCAP2 | Port VC Capability Register 2                            | 00000000h                   | RO               |

| 10Ch-10D  | PVCCTL  | Port VC Control                                          | 0000h                       | RO               |

| 10Eh-10Fh | PVCSTS  | Port VC Status                                           | 0000h                       | RO               |

| 110h-103h | VC0CAP  | VC0 Resource Capability                                  | 00000000h                   | RO               |

| 114h–117h | VC0CTL  | VC0 Resource Control                                     | 800000FFh                   | R/W, RO          |

| 11Ah-11Bh | VC0STS  | VC0 Resource Status                                      | 0000h                       | RO               |

| 11Ch-11Fh | VCiCAP  | VCi Resource Capability                                  | 00000000h                   | RO               |

| 120h-123h | VCiCTL  | VCi Resource Control                                     | 00000000h                   | R/W, RO          |

| 126h-127h | VCiSTS  | VCi Resource Status                                      | 0000h                       | RO               |

| 130h–133h | RCCAP   | Root Complex Link Declaration Enhanced Capability Header | 00010005h                   | RO               |

| 134h–137h | ESD     | Element Self Description                                 | 0F000100h                   | RO               |

| 140h–143h | L1DESC  | Link 1 Description                                       | 00000001h                   | RO               |

| 148h-14Bh | L1ADDL  | Link 1 Lower Address                                     | See Register                | RO               |

|           | 217.002 |                                                          | Description                 |                  |

# 1.1.1 VID—Vendor Identification Register (Intel® High Definition Audio Controller—D27:F0)

Offset: 00h-01h Attribute: RO

Default Value: 8086h Size: 16 bits

| Bit  | Description                                                                        |

|------|------------------------------------------------------------------------------------|

| 15:0 | <b>Vendor ID</b> — RO. This is a 16-bit value assigned to Intel. Intel VID = 8086h |

### 1.1.2 DID—Device Identification Register (Intel® High Definition Audio Controller—D27:F0)

Offset Address: 02h–03h Attribute: RO

Default Value: See bit description Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | Device ID — RO. This is a 16-bit value assigned to the Intel <sup>®</sup> ICH7 Intel <sup>®</sup> High Definition Audio controller. Refer to the <i>Intel</i> <sup>®</sup> I/O Controller Hub 7 (ICH7) Family Specification Update for the value of the Device ID Register. |

# 1.1.3 PCICMD—PCI Command Register (Intel® High Definition Audio Controller—D27:F0)

Offset Address: 04h–05h Attribute: R/W, RO Default Value: 0000h Size: 16 bits

| Bit   | Description                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | Reserved                                                                                                                                                                                                                                         |

| 10    | Interrupt Disable (ID) — R/W.  0= The INTx# signals may be asserted.  1= The Intel <sup>®</sup> High Definition Audio controller's INTx# signal will be de-asserted  NOTE: This bit does not affect the generation of MSIs.                      |

| 9     | Fast Back to Back Enable (FBE) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                            |

| 8     | SERR# Enable (SERR_EN) — R/W. SERR# is not generated by the ICH7 Intel High Definition Audio Controller.                                                                                                                                         |

| 7     | Wait Cycle Control (WCC) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                                  |

| 6     | Parity Error Response (PER) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                               |

| 5     | VGA Palette Snoop (VPS). Not implemented. Hardwired to 0.                                                                                                                                                                                        |

| 4     | Memory Write and Invalidate Enable (MWIE) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                 |

| 3     | Special Cycle Enable (SCE). Not implemented. Hardwired to 0.                                                                                                                                                                                     |

| 2     | Bus Master Enable (BME) — R/W. Controls standard PCI Express* bus mastering capabilities for Memory and I/O, reads and writes. Note that this bit also controls MSI generation since MSIs are essentially Memory writes.  0 = Disable 1 = Enable |

| 1     | Memory Space Enable (MSE) — R/W. Enables memory space addresses to the Intel High Definition Audio controller.  0 = Disable 1 = Enable                                                                                                           |

| 0     | I/O Space Enable (IOSE)—RO. Hardwired to 0 since the Intel High Definition Audio controller does not implement I/O space.                                                                                                                        |

# 1.1.4 PCISTS—PCI Status Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Offset Address: 06h–07h Attribute: RO, R/WC Default Value: 0010h Size: 16 bits

| Bit  | Description                                                                                                                                                                                                                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | Detected Parity Error (DPE) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                                                                                                                                               |

| 14   | SERR# Status (SERRS) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                                                                                                                                                      |

| 13   | Received Master Abort (RMA) — R/WC. Software clears this bit by writing a 1 to it.  0 = No master abort received.  1 = The Intel <sup>®</sup> High Definition Audio controller sets this bit when, as a bus master, it receives a master abort. When set, the Intel High Definition Audio controller clears the run bit for the channel that received the abort. |

| 12   | Received Target Abort (RTA) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                                                                                                                                               |

| 11   | Signaled Target Abort (STA) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                                                                                                                                               |

| 10:9 | DEVSEL# Timing Status (DEV_STS) — RO. Does not apply. Hardwired to 0.                                                                                                                                                                                                                                                                                            |

| 8    | Data Parity Error Detected (DPED) — RO. Not implemented. Hardwired to 0.                                                                                                                                                                                                                                                                                         |

| 7    | Fast Back to Back Capable (FB2BC) — RO. Does not apply. Hardwired to 0.                                                                                                                                                                                                                                                                                          |

| 6    | Reserved.                                                                                                                                                                                                                                                                                                                                                        |

| 5    | 66 MHz Capable (66MHZ_CAP) — RO. Does not apply. Hardwired to 0.                                                                                                                                                                                                                                                                                                 |

| 4    | Capabilities List (CAP_LIST) — RO. Hardwired to 1. Indicates that the controller contains a capabilities pointer list. The first item is pointed to by looking at configuration offset 34h.                                                                                                                                                                      |

| 3    | Interrupt Status (IS) — RO.  0 = This bit is 0 after the interrupt is cleared.  1 = This bit is 1 when the INTx# is asserted.  Note that this bit is not set by an MSI.                                                                                                                                                                                          |

| 2:0  | Reserved.                                                                                                                                                                                                                                                                                                                                                        |

# 1.1.5 RID—Revision Identification Register (Intel® High Definition Audio Controller—D27:F0)

Offset: 08h Attribute: RO Default Value: See bit description Size: 8 Bits

| Bit | Description                                                                                                                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Revision ID — RO. Refer to the $Intel^{\circledR}$ I/O Controller Hub 7 (ICH7) Family Specification Update for the value of the Revision ID Register. |

#### 1.1.6 PI—Programming Interface Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Offset: 09h Attribute: RO Default Value: 00h Size: 8 bits

| Bit | Description                 |

|-----|-----------------------------|

| 7:0 | Programming Interface — RO. |

### 1.1.7 SCC—Sub Class Code Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 0Ah Attribute: RO Default Value: 03h Size: 8 bits

| Bit | Description                                   |

|-----|-----------------------------------------------|

| 7:0 | Sub Class Code (SCC) — RO. 03h = Audio Device |

#### 1.1.8 BCC—Base Class Code Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 0Bh Attribute: RO Default Value: 04h Size: 8 bits

| Bit | Description                                         |

|-----|-----------------------------------------------------|

| 7:0 | Base Class Code (BCC) — RO. 04h = Multimedia device |

#### 1.1.9 CLS—Cache Line Size Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset:0ChAttribute:R/WDefault Value:00hSize:8 bits

| Bit | Description                                                                                   |

|-----|-----------------------------------------------------------------------------------------------|

| 7:0 | Cache Line Size — R/W. Implemented as R/W register, but has no functional impact to the ICH7. |

#### 1.1.10 LT—Latency Timer Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 0Dh Attribute: RO Default Value: 00h Size: 8 bits

| Bit | Description                         |  |

|-----|-------------------------------------|--|

| 7:0 | Latency Timer — RO. Hardwired to 00 |  |

#### 1.1.11 HEADTYP—Header Type Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 0Eh Attribute: RO Default Value: 00h Size: 8 bits

| Bit | Description                        |  |

|-----|------------------------------------|--|

| 7:0 | Header Type — RO. Hardwired to 00. |  |

# 1.1.12 HDBARL—Intel<sup>®</sup> High Definition Audio Lower Base Address Register (Intel<sup>®</sup> High Definition Audio—D27:F0)

Address Offset: 10h-13h Attribute: R/W, RO Default Value: 00000004h Size: 32 bits

| Bit   | Description                                                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:14 | <b>Lower Base Address (LBA)</b> — R/W. This field contains the base address for the Intel <sup>®</sup> High Definition Audio controller's memory mapped configuration registers; 16 KB are requested by hardwiring bits 13:4 to 0s. |

| 13:4  | RO. Hardwired to 0's                                                                                                                                                                                                                |

| 3     | Prefetchable (PREF) — RO. Hardwired to 0 to indicate that this BAR is NOT prefetchable.                                                                                                                                             |

| 2:1   | Address Range (ADDRNG) — RO. Hardwired to 10b, indicating that this BAR can be located anywhere in 64-bit address space.                                                                                                            |

| 0     | Space Type (SPTYP) — RO. Hardwired to 0. Indicates this BAR is located in memory space.                                                                                                                                             |

# 1.1.13 HDBARU—Intel<sup>®</sup> High Definition Audio Upper Base Address Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 14h-17h Attribute: R/W Default Value: 00000000h Size: 32 bits

| Bit  | Description                                                                                                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | <b>Upper Base Address (UBA)</b> — R/W. This field provides the upper 32 bits of the Base address for the Intel <sup>®</sup> High Definition Audio controller's memory mapped configuration registers. |

#### 1.1.14 SVID—Subsystem Vendor Identification Register (Intel® High Definition Audio Controller—D27:F0)

Address Offset: 2Ch–2Dh Attribute: R/WO Default Value: 0000h Size: 16 bits

The SVID register, in combination with the Subsystem ID register (D27:F0:2Eh), enable the operating environment to distinguish one audio subsystem from the other(s).

This register is implemented as write-once register. Once a value is written to it, the value can be read back. Any subsequent writes will have no effect.

This register is not affected by the D3<sub>HOT</sub> to D0 transition.

| Bit  | Description                 |

|------|-----------------------------|

| 15:0 | Subsystem Vendor ID — R/WO. |

#### 1.1.15 SID—Subsystem Identification Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 2Eh–2Fh Attribute: R/WO Default Value: 0000h Size: 16 bits

The SID register, in combination with the Subsystem Vendor ID register (D27:F0:2Ch) make it possible for the operating environment to distinguish one audio subsystem from the other(s).

This register is implemented as write-once register. Once a value is written to it, the value can be read back. Any subsequent writes will have no effect.

This register is not affected by the D3<sub>HOT</sub> to D0 transition.

|   | Bit  | Description          |

|---|------|----------------------|

| I | 15:0 | Subsystem ID — R/WO. |

#### 1.1.16 CAPPTR—Capabilities Pointer Register (Audio—D30:F2)

Address Offset: 34h Attribute: RO Default Value: 50h Size: 8 bits

This register indicates the offset for the capability pointer.

| Bit | Description                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Capabilities Pointer (CAP_PTR) — RO. This field indicates that the first capability pointer offset is offset 50h (Power Management Capability). |

### 1.1.17 INTLN—Interrupt Line Register (Intel® High Definition Audio Controller—D27:F0)

Address Offset: 3Ch Attribute: R/W Default Value: 00h Size: 8 bits

| Bit | Description                                                                                                                                                                                  |   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 7:0 | <b>Interrupt Line (INT_LN)</b> — R/W. This data is not used by the Intel <sup>®</sup> ICH7. It is used to communicate to software the interrupt line that is connected to the interrupt pin. | 1 |

### 1.1.18 INTPN—Interrupt Pin Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 3Dh Attribute: RO Default Value: See Description Size: 8 bits

| Bit | Description                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved.                                                                                                   |

| 3:0 | Interrupt Pin — RO. This reflects the value of D27IP.ZIP (Chipset Config Registers:Offset 3110h: bits 3:0). |

# 1.1.19 HDCTL—Intel<sup>®</sup> High Definition Audio Control Register (Intel<sup>®</sup> High Definition Audio Controller—D27:F0)

Address Offset: 40h Attribute: R/W, RO Default Value: 00h Size: 8 bits

| Bit | Description                                                                                                                                                                                                                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Reserved.                                                                                                                                                                                                                                                                                                   |

|     | BITCLK Detect Clear (CLKDETCLR) — R/W.                                                                                                                                                                                                                                                                      |

|     | 0 = Clock detect circuit is operational and maybe enabled.                                                                                                                                                                                                                                                  |

| 3   | 1 = Writing a 1 to this bit clears bit 1 (CLKDET#) in this register. CLKDET# bit remains clear when this bit is set to 1.                                                                                                                                                                                   |

|     | <b>NOTE:</b> This bit is not affected by the D3 <sub>HOT</sub> to D0 transition.                                                                                                                                                                                                                            |

|     | BITCLK Detect Enable (CLKDETEN) — R/W.                                                                                                                                                                                                                                                                      |

|     | 0 = Latches the current state of bit 1 (CLKDET#) in this register                                                                                                                                                                                                                                           |

| 2   | 1 = Enables the clock detection circuit                                                                                                                                                                                                                                                                     |

|     | <b>NOTE:</b> This bit is not affected by the D3 <sub>HOT</sub> to D0 transition.                                                                                                                                                                                                                            |

|     | BITCLK Detected Inverted (CLKDET#) — RO. This bit is modified by hardware.                                                                                                                                                                                                                                  |

|     | It is set to 0 when the Intel <sup>®</sup> ICH7 detects that the BITCLK is toggling, indicating the presence of an AC'97 codec on the link                                                                                                                                                                  |

| 1   | NOTES:  1. Bit 2 (CLKDETEN) and bit 3 (CLKDETCLR) in this register control the operation of this bit and must be manipulated correctly in order to get a valid CLKDET# indicator.  2. This bit is not affected by the D3 <sub>HOT</sub> to D0 transition.                                                   |

|     | Intel® High Definition Audio/AC '97 Signal Mode — R/W. This bit selects the shared Intel High Definition Audio/AC '97 signals.                                                                                                                                                                              |

|     | 0 = AC '97 mode is selected (Default)                                                                                                                                                                                                                                                                       |

|     | 1 = Intel High Definition Audio mode is selected                                                                                                                                                                                                                                                            |

| 0   | NOTES:  1. This bit has no effect on the visibility of the Intel High Definition Audio and AC '97 function configuration space.  2. This bit is in the resume well and only clear on a power-on reset. Software must not makes assumptions about the reset state of this bit and must set it appropriately. |

# 1.1.20 TCSEL—Traffic Class Select Register (Intel® High Definition Audio Controller—D27:F0)

Address Offset: 44h Attribute: R/W Default Value: 00h Size: 8 bits

This register assigned the value to be placed in the TC field. CORB and RIRB data will always be assigned TC0.

| Bit | Description                                                                                                                                                                                                                                                                                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | Reserved.                                                                                                                                                                                                                                                                                            |

| 2:0 | Intel® HIgh Definition Audio Traffic Class Assignment (TCSEL)— R/W. This register assigns the value to be placed in the Traffic Class field for input data, output data, and buffer descriptor transactions.  000 = TC0  001 = TC1  010 = TC2  011 = TC3  100 = TC4  101 = TC5  110 = TC6  111 = TC7 |

|     | <b>NOTE</b> : These bits are not reset on D3 <sub>HOT</sub> to D0 transition; however, they are reset by PLTRST#.                                                                                                                                                                                    |

# 1.1.21 DCKSTS—Docking Status Register (Intel® High Definition Audio Controller—D27:F0)

Address Offset: 4Dh Attribute: R/WO, RO Default Value: 80h Size: 8 bits

| Bit | Description                         |

|-----|-------------------------------------|

| 7   | BIOS is required to clear this bit. |

| 6:1 | Reserved.                           |

| 0   | Reserved.                           |

# 1.1.22 PID—PCI Power Management Capability ID Register (Intel® High Definition Audio Controller—D27:F0)

Address Offset:50h-51hAttribute:RODefault Value:6001hSize:16 bits

| Bit  | Description                                                                                            |

|------|--------------------------------------------------------------------------------------------------------|

| 15:8 | Next Capability (Next) — RO. Hardwired to 60h. Points to the next capability structure (MSI).          |